# CRC – BASED HARDWARE TROJAN DETECTION FOR IMPROVED HARDWARE SECURITY

A Project report submitted in partial fulfillment of the requirements for the award of the degree of

**BACHELOR OF TECHNOLOGY**

IN

**ELECTRONICS AND COMMUNICATION ENGINEERING**

Submitted by

M.Laxmipriya (317126512087) V.L.S.J.Raja (317126512120) Ch.Hemasundar (317126512072) Ch.Mounika (318126512L16)

Under the guidance of

Mr.P.Devi Pradeep

**Assistant Professor**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY AND SCIENCES

(Permanently Affiliated to AU, Approved by AICTE and Accredited by NBA & NAAC

with 'A' Grade)

Sangivalasa, Bheemili mandal, Visakhapatnam Dist.(A.P)-531162

2020-2021

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY AND SCIENCES (Permanently Affiliated to AU, Approved by AICTE and Accredited by NBA & NAAC with 'A' Grade)

Sangivalasa, Bheemili Mandal, Visakhapatnam dist.(A.P)-531162

# CERTIFICATE

This is to certify that the project report entitled "CRC-Based Hardware Trojan Detection For Improved Hardware Security" submitted by M.Laxmipriya (317126512087), V.L.S.J.Raja (317126512120), Ch.Hemasundar (317126512072), Ch.Mounika (318126512L16) in partial fulfillment of the requirements for the award of the degree of Bachelor of Technology in Electronics & Communication Engineering of Andhra University, Visakhapatnam is a record of bonafide work carried out under my guidance and supervision.

Project Guide

Denric

Mr.P.Devi Pradeep Asst. Professor Department of E.C.E ANITS

Assistant Professor Department of E.C.E. Anil Neerukonda Institute of Technology & Sciences Sangivalaro, Visukhapatna 1001 102 Head of the Department  $\mathcal{P}$  '

Dr. V.Rajyalakshmi Department of E.C.E

ANITS

Head of the Department Department of E C E Anil Neerukonda Institute of Technology & Sciences Sangivalasa - 531 162

# ACKNOWLEDGEMENT

We would like to express our deep gratitude to our project guide **Mr.P.Devi Pradeeep Assistant Professor**, Department of Electronics and Communication Engineering, ANITS, for his guidance with unsurpassed knowledge and immense encouragement. We are grateful to **Dr.V.Rajyalakshmi**, Head of the Department, Electronics and Communication Engineering, for providing us with the required facilities for the completion of the project work.

We are very much thankful to the **Principal and Management**, **ANITS**, **Sangivalasa**, for their encouragement and cooperation to carry out this work.

We express our thanks to all **teaching faculty** of Department of ECE, whose suggestions during reviews helped us in accomplishment of our project. We would like to thank **all non-teaching staff** of the Department of ECE, ANITS for providing great assistance in accomplishment of our project.

We would like to thank our parents, friends, and classmates for their encouragement throughout our project duration. At last but not the least, we thank everyone for supporting us directly or indirectly in completing this project successfully.

#### **PROJECT BATCH STUDENTS**

M. Laxmipriya(317126512087)

V.L.S.J.Raja(317126512120)

Ch.Hemasundar(317126512072)

Ch.Mounika(318126512L16)

# CONTENTS

| ABSTRACT                        | vi  |

|---------------------------------|-----|

| LIST OF FIGURES                 | vii |

| LIST OF TABLES                  | Х   |

| LIST OF ABBREVATIONS            | xi  |

| CHAPTER 1 INTRODUCTION          | 01  |

| 1.1 Project Objective           | 01  |

| 1.2 Background                  | 01  |

| 1.3 Motivation                  | 03  |

| 1.4 Project Outline             | 06  |

| CHAPTER 2 HARDWARE SECURITY     | 07  |

| 2.1 Introduction                | 07  |

| 2.2 Attacks on Hardware         | 08  |

| 2.3 Attack Circuits             | 09  |

| 2.4 Counter Measures            | 10  |

| 2.5 Hardware Trojan             | 10  |

| 2.5.1 Action Characteristics    | 11  |

| 2.5.2 Payload Characteristics   | 14  |

| 2.5.3 Trojans in CLB/EMB FPGA   | 15  |

| 2.5.4 Types of Hardware Trojans | 17  |

| 2.5.5 Example Attack            | 17  |

| 2.6 Real Life Implementation    | 18  |

| CHAPTER 3 INTRODUCTION TO FPGA  | 20  |

| 3.1 What is FPGA?               | 20  |

| 3.2 Theory                      | 20  |

| 3.3 Overview of FPGA            | 26  |

| 3.4 Programmability of FPGAs    | 28  |

| 3.5 FPGA Logic Blocks                             | 29 |

|---------------------------------------------------|----|

| 3.6 Modern FPGAs                                  | 31 |

| CHAPTER 4 VERILOG HDL                             | 32 |

| 4.1 What is HDL?                                  | 32 |

| 4.2 Importance of HDLs                            | 32 |

| 4.3 Introduction to Verilog HDL                   | 32 |

| 4.4 Module                                        | 33 |

| 4.5 Tokens of Verilog                             | 33 |

| 4.5.1 Case Sensitivity                            | 34 |

| 4.5.2 Keywords                                    | 34 |

| 4.5.3 Operators                                   | 34 |

| 4.5.4 Data Types                                  | 34 |

| 4.5.5 Comments                                    | 36 |

| 4.5.6 Number Specification                        | 36 |

| 4.6 Module declaration                            | 37 |

| 4.6.1 Module Instantiation                        | 38 |

| 4.7 Flow Chart of Verilog                         | 40 |

| 4.8 Software Tools Used                           | 43 |

| CHAPTER 5 HARDWARE TROJAN INSERTION AND DETECTION | 51 |

| 5.1 Hardware Trojan                               | 51 |

| 5.2 Algorithm for Trojan Detection                | 51 |

| 5.3 Hardware Trojan Detection Methodologies       | 51 |

| 5.3.1 Visual Detection                            | 52 |

| 5.3.2 Logic Based Testing                         | 52 |

| 5.3.3 Side Channel Analysis                       | 53 |

| 5.3.4 CRC(Cyclic Redundancy Check)                | 53 |

| <b>CHAPTER 6 CONCLUSION AND FUTURE WORK</b>       | 62 |

| REFERENCES                                        | 63 |

### ABSTRACT

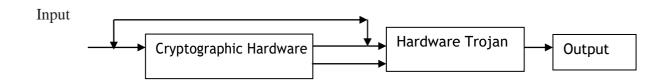

One of the most important problems to resolve nowadays is hardware Trojan circuits. End-users need to get guarantees that their devices are reliable enough, are not controlled by unknown entities, and will not leak sensitive information. Several methodologies help at solving the problems of hardware Trojans through the help of "Golden reference", which is not always available. This arises the need for an efficient method called as CRC. This is a logic based detection procedure which avoids the requirements of complex pre-processing procedures like fingerprinting, thermal imaging, segmentation etc. First, a counter based Trojan is designed and simulated functionally by XILINX VIVADO 2020.2. This Trojan is designed in Verilog HDL, which is used to target UART module of FPGA onboard. Payload of the Trojan is to corrupt the transmitted frame after trigger gets activated. Then, CRC algorithm which is designed in verilog HDL is simulated and implemented on ARTIX-7 Starter Kit Board. This work involves the detection of Hardware Trojan in a circuit using an improved voting algorithm employing CRC(Cyclic Redundancy Check). This logic based detection procedure avoids the requirements of complex pre-processing procedures like segmentation, fingerprinting, thermal imaging etc. Detection accuracy of this CRC method is found to be 95.27% based on detailed analysis with infected and non-infected circuits.

# LIST OF FIGURES

| Fig 1.1  | (a) General model of a hardware Trojan circuit realized through malicious modification of a hardware. | 2  |

|----------|-------------------------------------------------------------------------------------------------------|----|

|          | (b) An example of combinational Trojan.                                                               |    |

|          | (c) An example of sequential Trojan.                                                                  |    |

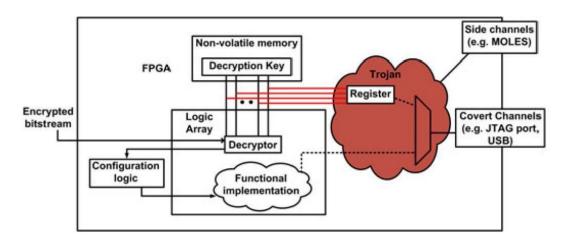

| Fig 2.1  | Block Diagram of Hardware Trojan Inserted Circuit                                                     | 11 |

| Fig 2.2  | Simplified architecture of an FPGA showing the trigger points that a Trojan may use.                  | 13 |

| Fig 2.3  | Simplified schematic of digital clock manager (DCM) in Xilinx's Virtex-5 FPGA device                  | 13 |

| Fig 2.4  | Diagram showing examples of payloads that can be altered by an implanted Trojan circuit.              | 14 |

| Fig 2.5  | Programmable I/O block containing hardware Trojans to cause logical and electrical malfunction.       | 16 |

| Fig 2.6  | FPGA device with security features for bitstream decryption.                                          | 16 |

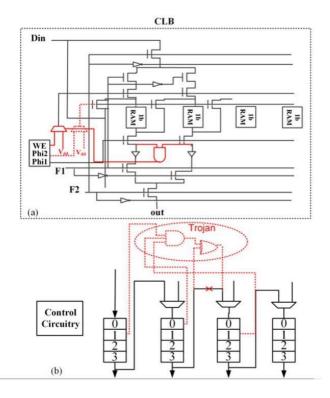

| Fig 2.7  | Hardware Trojan inside:                                                                               |    |

|          | (a) A Configurable Logic Block (CLB) and                                                              |    |

|          | (b) An Embedded Memory Block (EMB) of FPGA.                                                           | 17 |

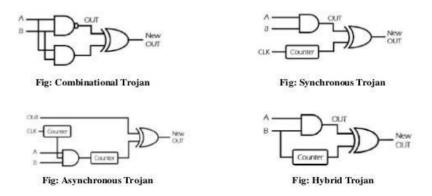

| Fig 2.8  | Types of Hardware Trojans                                                                             | 17 |

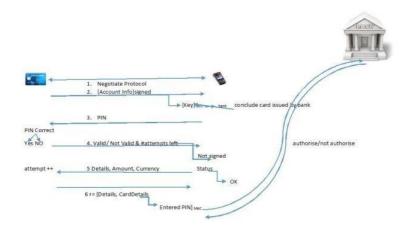

| Fig 2.9  | Simplified diagram of Protocol used                                                                   | 18 |

| Fig 2.10 | The Attack                                                                                            | 18 |

| Fig 2.11 | Real life implementation of Chin & Pin attack                                                         | 19 |

| Fig 3.1  | Xilinx Artix 7 FPGA Trainer kit                                                                       | 21 |

| Fig 3.2  | Port numbers of Artix7 FPGA Trainer kit                                                               | 21 |

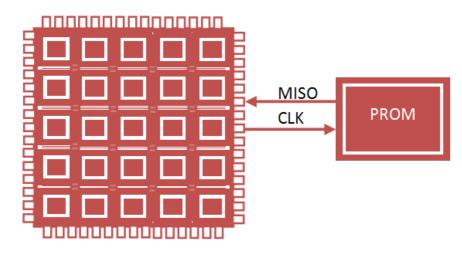

| Fig 3.3  | FPGA Configure through External PROM                                                                  | 24 |

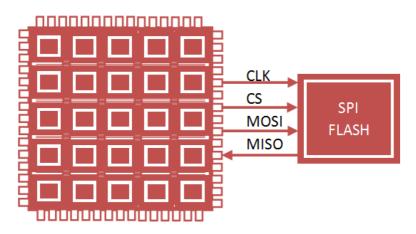

| Fig 3.4  | FPGA Configure through SPI FLASH Memory                 | 24 |

|----------|---------------------------------------------------------|----|

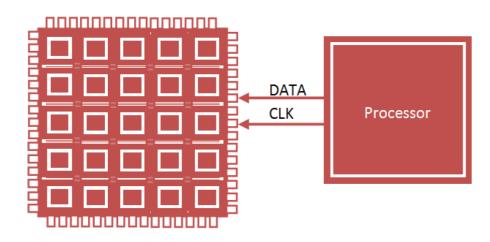

| Fig 3.5  | FPGA Configure through Internal FLASH                   | 25 |

| Fig 3.6  | Slave Mode                                              | 25 |

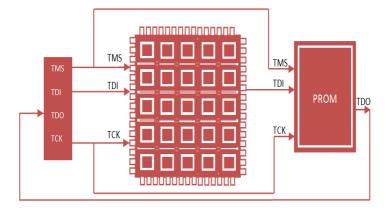

| Fig 3.7  | JTAG connection                                         | 26 |

| Fig 3.8  | Block diagram of FPGA                                   | 28 |

| Fig 3.9  | Schematic diagram of FPGA Logic blocks                  | 30 |

| Fig 3.10 | Schematic diagram of Coarse grain block                 | 30 |

| Fig 3.11 | Schematic diagram of FPGA Design flow                   | 31 |

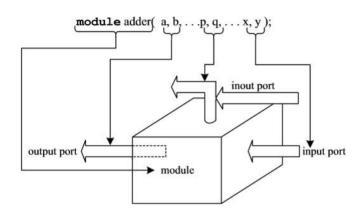

| Fig 4.1  | Representation of a module as black box with its ports. | 33 |

| Fig 4.2  | Illustration of Scalars and Vectors                     | 35 |

| Fig 4.3  | Flowchart representation of Verilog Code                | 40 |

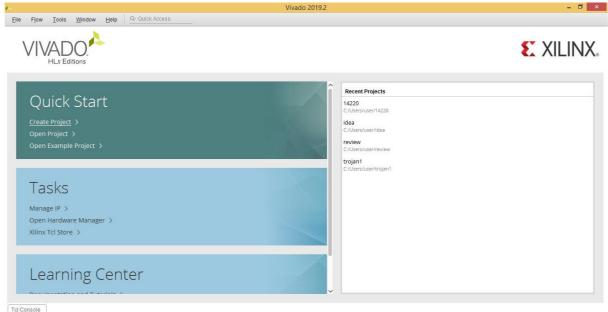

| Fig 4.4  | Opening window of Xilinx 2019.2                         | 44 |

| Fig 4.5  | Create project window                                   | 45 |

| Fig 4.6  | Name and Location entry for project                     | 45 |

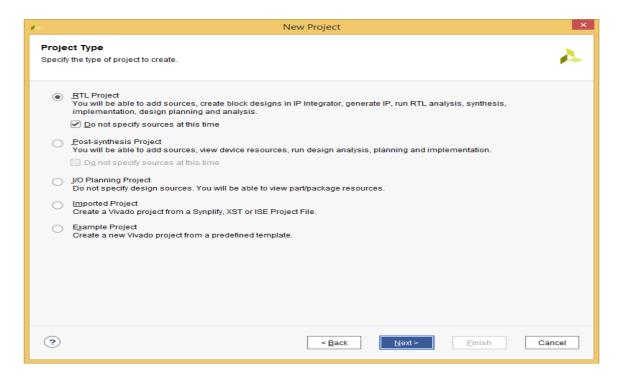

| Fig 4.7  | Selecting type of the project                           | 46 |

| Fig 4.8  | Specifications window for the project                   | 46 |

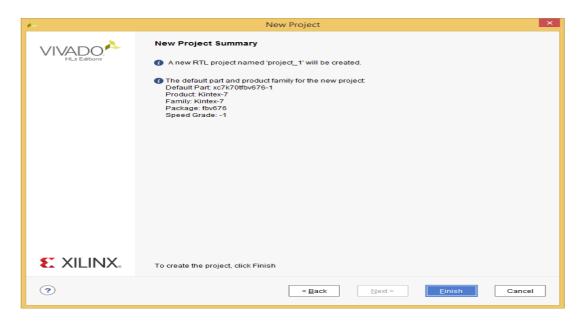

| Fig 4.9  | Summary window of the project                           | 47 |

| Fig 4.10 | Add sources                                             | 47 |

| Fig 4.11 | Creating source                                         | 48 |

| Fig 4.12 | Creating file window                                    | 48 |

| Fig 4.13 | Filename creation window                                | 49 |

| Fig 4.14 | Sources window                                          | 49 |

| Fig 4.15 | Sidebar for performing required process.                | 50 |

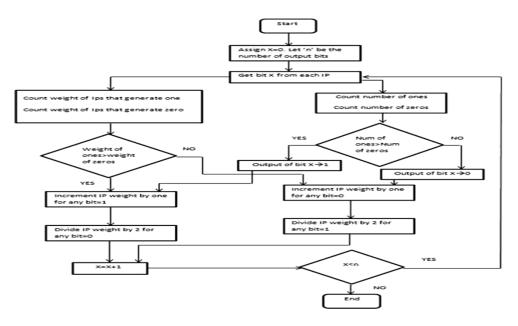

| Fig 5.1 | Flowchart of Modified voting algorithm                         | 54 |

|---------|----------------------------------------------------------------|----|

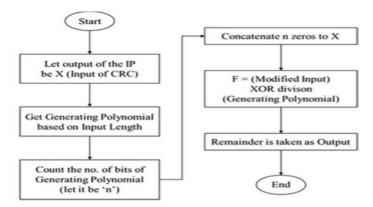

| Fig 5.2 | Simple outline for CRC                                         | 55 |

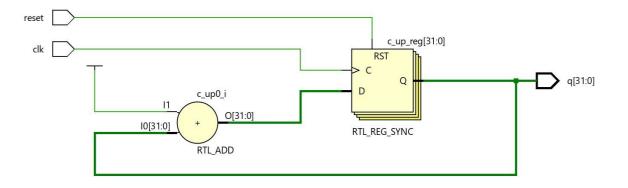

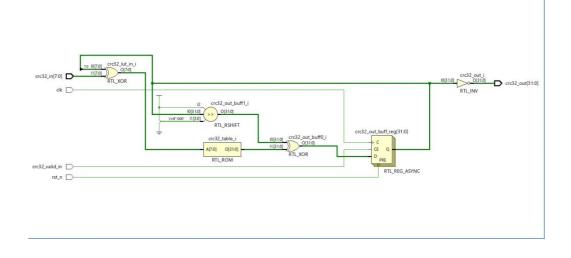

| Fig 5.3 | RTL schematic diagram for counter based sequential Trojan      | 56 |

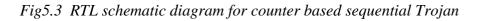

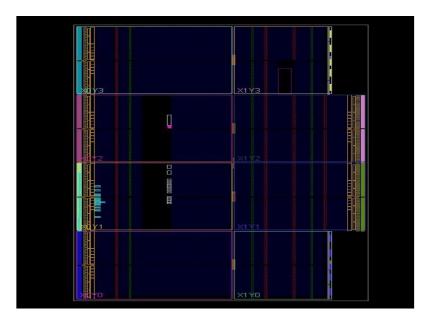

| Fig 5.4 | Floor planning of counter based sequential Trojan circuit      | 56 |

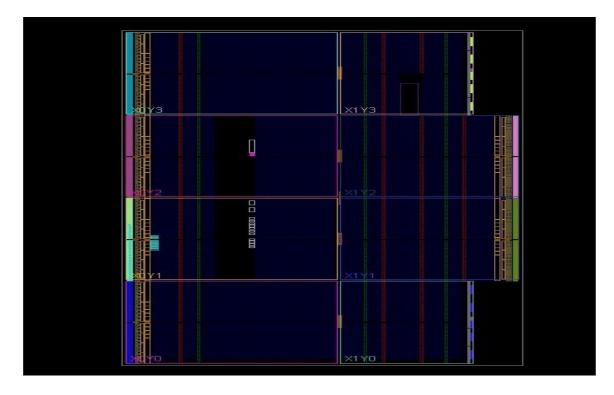

| Fig 5.5 | Simulation results for counter based sequential Trojan circuit | 57 |

| Fig 5.6 | RTL schematic diagram for Trojan detection circuit             | 59 |

| Fig 5.7 | Floor planning of Trojan detection circuit                     | 59 |

| Fig 5.8 | Simulation result for Trojan detection circuit                 | 60 |

# LIST of TABLES

| Table 3.1 | Artix-7 FPGA Feature Summary by Device                    | 22 |

|-----------|-----------------------------------------------------------|----|

| Table 3.2 | Artix-7 FPGA Device-Package Combinations and Maximum I/Os | 22 |

| Table 3.3 | Comparison between programming techniques                 | 29 |

| Table 5.1 | Synthesis report for Trojan Insertion                     | 58 |

| Table 5.2 | Synthesis report for Trojan Detection                     | 60 |

# LIST OF ABBREVATIONS

| HT     | Hardware Trojan                                   |

|--------|---------------------------------------------------|

| HTT    | Hardware Trojan Threat                            |

| FPGA   | Field Programmable Gate Array                     |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| CLB    | Configurable Logic Blocks                         |

| EMB    | Embedded Memory Blocks                            |

| HDL    | Hardware Description Language                     |

# Chapter 1

#### **INTRODUCTION**

Nowadays, hardware Trojan protection became a hot topic especially after the horizontal silicon industry business model. Third party IP is the building block of many critical systems and that arise a question of confidentiality and reliability of these blocks. In this work, we present novel methods for system protection and Trojan detection that alleviate the need for a golden chip. In addition, we introduce a scenario to dynamically remove infected IPs embedded on FPGAs. In this project side-channel analysis and ring oscillator based approaches were used to detect Hardware Trojan. Dynamic Trojan detection is done using multiple variant voting. Different methodologies can be implemented for different Trojans.

#### **1.1 Project Objective**

The main objective of the project is to insert a hardware Trojan and detect it using various methods and thereby compare which type of Trojan is detected efficiently by which type of methods. The hardware Trojan is nothing but a malicious circuit which is placed in the integrated chip without affecting its normal functionality. All these detection methods are followed by a flow of process specified as an algorithm in chapter5.Everytime the Trojan inserted circuit parameters are compared with the golden circuit and then judge if Trojan is present or not.

Simulation results are obtained for different circuits which are in Chapter 5.

#### **1.2 Background**

Malicious modifications of integrated circuits, referred to as Hardware Trojans, have emerged as a major security threat due to widespread outsourcing of IC manufacturing to un-trusted foundries. An adversary can potentially tamper with a design in these fabrication facilities by inserting malicious circuitry, leading to potentially catastrophic malfunctions in security-critical application domains, such as the military, government, communications, space, and medicine. Conventional post-manufacturing testing, test generation algorithms, and test coverage metrics often fail to detect Hardware Trojans due to their diversity, complexity, and rare triggering conditions. An intelligent adversary can design a Trojan to only trigger under very rare conditions on an internal node, which is unlikely to arise during post-manufacturing test, but can be triggered during long hours of in-field operation.

The detection of Trojans by employing side-channel parameters, such as power trace or delay overhead, is limited due to the large process variations in nano scale IC technologies, detection sensitivities of small Trojans, and measurement noise. Often these issues mask the effect of Trojan circuits, especially for ultra small Trojans. From an adversary's perspective, the desired features for a successful Trojan are as follows: rarely activated to evade logic based testing, low overhead to evade side-channel based detection approach, and low side-channel signature to evade Design for Security (DfS) hardening mechanisms. The

condition of Trojan activation is referred to as the trigger, and the node affected by the Trojan is referred to as its payload. Trojans can be classified based on their triggering conditions or payload mechanisms. The trigger mechanism can be either digital or analog. Digitally triggered Trojans can be classified into combinational and sequential Trojans. Trojan can also be classified into digital and analog based on the payload mechanisms. Digital Trojans invert the logic values at internal nodes or modify the contents of memory locations, while the analog payload Trojans may affect circuit parameters, such as performance, power, and noise margin.

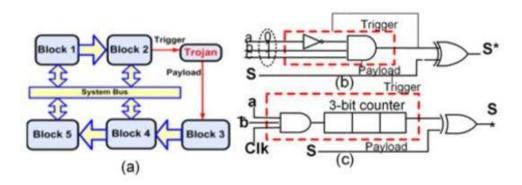

A combinational Trojan is activated on the simultaneous occurrences of a particular condition at certain internal nodes, while a sequential Trojan acts as a time-bomb, exhibiting its malicious effect due to a sequence of rare events after a long period of operation. Fig 1.1(a) illustrates the general scenario of a Trojan attack in a design, where a Trojan is realized through the malicious modification of the circuit with a trigger condition and payload. Fig 1.1 (b) shows an example of combinational Trojan which does not contain any sequential elements, and depends only on the simultaneous occurrence of a set of rare node conditions. Conversely, the sequential Trojans shown in Fig 1.1 (c) undergo a sequence of state transitions before triggering a malfunction. The 3-bit counter causes a malfunction at the node S on reaching a particular count, and the count is increased only when the condition a = 1, b = 0 is satisfied at the positive clock-edge. Protection against hardware Trojan has been widely explored by researchers. These approaches are based on the following three approaches:

(1) Specialized functional testing that rely on triggering an unknown Trojan and observing its effect in output ports of a design;

(2) side-channel analysis that rely on observing a Trojan effect in physical parameters, such as supply current or path delay and

(3) design/integration approaches that either prevent a Trojan insertion or facilitate detection during production test.

*Fig1.1 (a) General model of a hardware Trojan circuit realized through malicious modification of a hardware. (b) An example of combinational Trojan. (c) An example of sequential Trojan.*

#### **1.3 Motivation**

The main idea for working on hardware Trojan detection is to control the cyber crimes to the maximum extent. For example, in the year 2007 the backdoor built into a Syrian radar system was responsible for the system's failure. There are also reports of Trojans being used by the USSR to intercept American communications during the cold war. Time to activate a hardware Trojan circuit is a major concern from the authentication standpoint.

It is also a direct threat to the already vulnerable Internet of Things, meaning that wirelessenabled household devices also become potential targets. The problem is such that even previously 'reputable' factories are vulnerable to attacks, since all that is required is one employee to alter the existing code to include a Trojan. As most IC designs are extremely large and contain a huge amount of hardware description, these inclusions are difficult to detect and the sheer size of the code can require many people having access to the code at production level.

Regarding military grade products utilizing ICs, the problem of hardware Trojans is critical with the threat level of the Trojan being such that it could potentially be catastrophic. Malicious inclusions of code could cause life saving equipment to fail, missiles to lose control, and cryptography keys to be leaked. While incidents of hardware Trojans, are not openly discussed there have been a few noted. In 2007, it was assumed that a backdoor built into a Syrian radar system was responsible for the system's failure. There are also reports of Trojans being used by the USSR to intercept American communications during the cold war. The problem is aggravated further still when considered in relation to the growth in production of counterfeit goods. Such goods may be produced in less than reputable factories, so the inclusion of malicious code in the production process is far from unrealistic .As counterfeit goods are not generally sold through trustworthy channels, it is impossible to recall products found to be unsafe or indeed to produce updated firmware to deal with emerging threats. This can expose consumers to a plethora of malicious attacks by hackers. For example, a Trojan leaking cryptography keys in counterfeit IOT devices could potentially give hackers access to a network of devices that can be utilized in ' Mirai' like attacks and cannot be recalled or patched In this paper, a hardware Trojan is created and emulated on a consumer FPGA board. The experiments to detect the Trojan in a dormant and active state are made using off-the-shelf technologies which rely on thermal imaging, power monitoring, and side-channel analysis.

Unfortunately, those theories are not in nature groundless or out-with the realms of the possible. In fact several of them have already been instantiated. One such rumor of 'kill switches' being hidden in commercial processors was confirmed by an anonymous U.S. defence contractor who indicated the culprit to be a 'European Chip Maker' .The potential consequence of the existence of such a switch could be catastrophic. Indeed, as previously highlighted, this particular hardware Trojan was blamed for the failure of a Syrian radar to detect an incoming air strike for the Threat of the Hardware Trojan. The complexity and cost of the design of ICs has grown exponentially over the last decade as the semiconductor industry has scaled to sub-micron levels. A typical IC board will go through a rigorous process consisting of several stages. Firstly, the specifications must be translated into a behavioural description, usually in a hardware description language such as Verilog or VHDL. Once this has been completed, the next phase is to perform synthesis to transform the behavioural description into a design implementation using logic gates such as a net-list. Once the synthesis has been completed, the net-list is implemented as a layout design and the digital files are passed to the foundry for fabrication. As well as outsourcing the production of ICs, many companies are also purchasing third party intellectual property (IP) cores, and utilizing third party Electronic Design Automation (EDA) tools. Each use of third-party software presents a new opportunity for attacks such as hardware Trojan insertion, IP piracy, IC tampering, and IC cloning. Although these attacks are all of importance, the hardware Trojan is by far the most dangerous attack, and, as such, has garnered much attention. At Foundry Level As semiconductor technology has advanced, the cost of owning foundry has increased dramatically. In 2015, the cost was estimated to be in the region of 5 billion USD. As a direct result of this, many companies can no longer afford to fund the production process from start to finish, and are outsourcing their production to cheaper foreign foundries. Whilst undesirable modifications to ICs should ideally be detectable by pre-silicon verification and simulation, this would require a specific model of the entire IC design and this is not always readily available particularly where third party IP cores or EDA tools have been used. In addition, large multi module designs are rarely compliant with exhaustive verification.

Post silicone approaches to design verification include destructive de-packaging and reverse engineering of the IC. However, current techniques do not allow destructive verification of ICs to be scalable. It is also possible for an attacker to infect only a portion of the produced ICs, making these tests futile. Most post silicone logical testing techniques are also unsuitable for detecting hardware Trojans. This is attributed to the stealthy nature of the hardware Trojan and to the large numbers of differing taxonomy that can be employed by the attackers. Most hardware Trojans are programmed to activate under a specific set of conditions, and a skilled attacker would ensure that these conditions were undetectable by the testing routine. This is particularly true of Trojans targeting sequential finite state machines. Industries Affected Military Hardware Trojans are a huge threat to many industries. However, security conscious industries, such as the military, are in a particularly high risk bracket and defence departments are very aware of this. The U.S. Department of Defense (DoD) has created a "Trusted Foundry Program" to ensure its military equipment remains free of hardware Trojans by using only accredited foundries. This means that only American foundries which are located on the Americal soil and which underwent the strictest vetting process are allowed to work on the chips for the U.S. DoD. In addition to vetting the foundries, close attention is being paid to the other links in the design and supply chain. While this approach may seem effective, it has its limitations. The majority of western foundries are woefully behind their foreign counterparts when it comes to the level of technology they can provide. This seriously limits access to more advanced chips which are required for modern avionics and weapons systems.

If the attacker creates the Trojan through the modification of the existing code, then it will be classified as a parametric. Typically, this can be achieved by thinning wires or weakening transistors and flip flops. This type of Trojan is notoriously hard to detect as the alteration can be minuscule. The next physical characteristic the attacker would have to consider would be the size of the hardware Trojan. In this context, the size refers to the physical extension of the hardware Trojan or the number of components it consists of. In case of a large Trojan consisting of many components, an attacker can distribute these across the IC, placing components where they are necessary to execute their payload in accordance with the functions of the hardware Trojan. This is known as loose distribution. In contrast, a smaller hardware Trojan consisting of only a few components allows for the components to be placed together as they will occupy only a small part of the layout of the IC. This is known as tight distribution.

On rare occasions, a determined attacker could regenerate the layout to encompass the hardware Trojan, moving the components of the IC to accommodate the components of the hardware Trojan. This is referred to as a structural alteration Activation Characteristics Typically, a hardware Trojan will be condition- based, meaning that its activation will be dependent on a trigger defined by the attacker. The trigger itself will generally consist of either a predefined input pattern, or specific internal logic state, or counter value, and can be triggered both internally and externally. An externally triggered hardware Trojan will usually consist of malicious logic within the IC that utilizes an external sensor such as a radio antenna. The attacker will then communicate via the compromised component enabling them to trigger the antenna. It is easy to see why this can be extremely dangerous when it comes to security conscious industries such as the military. It is not out-with the realms of the believable to postulate that an attacker could feasibly re-route or switch off a missile via a radio signal as suggested.

Conversely, an internally triggered hardware Trojan will look within the circuitry for the set of conditions that will cause it to activate. A typical example of this would be countdown logic. In contrast to the condition-based Trojan that will only activate when its trigger conditions are met, the "always-on" Trojan is active from the moment of insertion, and relies on internal signals. This type of hardware Trojan is generally split into two categories; combinational and sequential. A combinational Trojan will activate upon detection of a specific set of circumstances within the internal signals of the IC. Sequential Trojans will also monitor the internal signals of the IC. However, instead of looking for a specific condition, they activate when a specific sequence of events occurs.

# 1.4 Project Outline

The project Hardware Insertion and Detection deals with the hardware security domain where securing information is vital in this sophisticated contemporary world. Day to day technology has been improving along with this the loop holes for hackers are becoming more and causing cyber security problems. In order to prevent and control these problems this project gives a scope to control the problems. By continuous analysis of the circuit the parameters like path delay can be found changed if Trojan is present.

A circuit is said to be Trojan affected if its parameters shows a significant change with the parameters of Trojan free circuit. The Trojan free circuit is called the golden circuit. Different Trojans can be detected using different methodologies. Most popular and effective methods are side channel analysis and ring oscillator based detection. All these circuits are simulated using Xilinx Vivado and reports were generated and the parameter were compared for Trojan free and Trojan effected circuit.

# **CHAPTER 2**

# HARDWARE SECURITY

# 2.1 Introduction

Hardware is a collection of physical elements that constitutes a computer system. Hardware is used by everyone even if they are not aware of it. Hardware in this context might be:

a. Computer Hardware: Some computer hardware are Processors, firmware, memory etc.

i. Processors: is the electronic circuitry within a computer that carries out the instructions of a computer program by performing the basic arithmetic, logical, control and input/output (I/O) operations specified by the instructions

ii. Firmware: is the combination of a hardware device, e.g. an integrated circuit, and computer instructions and data that reside as read only software on that device

iii. Memory: Memory refers to the device used to store information for use in a computer.

b. Mobile Hardware: Sim Card, RFID/Smart Card, Chip and Pin

i. Sim Card: is an integrated circuit that is intended to securely store the international mobile subscriber identity (IMSI) and the related key used to identify and authenticate subscribers on mobile telephony devices (such as mobile phones and computers).

**ii**. RFID: is the wireless use of electromagnetic fields to transfer data, for the purposes of automatically identifying and tracking tags attached to objects. For example, an RFID tag attached to an automobile during production can be used to track its progress through the assembly line.

iii. Smart Card: is any pocket-sized card with embedded integrated circuits. Smart cards are made of plastic, and can provide strong security authentication for single sign-on (SSO) with large organizations

iv Chip & Pin: "Chip" refers to a computer chip embedded in the smartcard, and "PIN" refers to a personal identification number that the customer must supply. "Chip and PIN" is also used in a generic sense to mean any EMV smart card technology that relies on an embedded chip and a PIN.

c. Future Hardware: PUFs (Physically Unclonable Functions) PUFs have a unique fingerprint in a physical object that means if you have an object with one fingerprint; another object with the same fingerprint cannot be created. It uses challenge/response for its operations. The challenge/response explains that if a message is sent to a physical object and the physical object is changed to another physical object, and same message is

sent to the second physical object, the two physical objects react differently because of their unique fingerprint.

# 2.2 Attacks on Hardware

1. **Physical Attacks:** The main thing that differentiates hardware attacks from software attacks is the physicality of the attack done with hardware tools. This raises the bar for hardware attacks because any attacker that wants to perform an attack on the hardware needs to have extensive knowledge of the hardware, unlike the software attacks that can be done by just downloading a vulnerability tool on the internet to perform attacks.

2. Generally, the hardware wants to protect a secret so the secret is embedded in a physical object. For example, the bank card wants to protect your pin, the pin is encoded in the card and if the attacker can probe the chip of the card and read the pin then the card is useless. The secret in the hardware should not be writable even though it provides the information on the card when placed on a terminal. If we consider STRIDE, we have to consider two main points: the Information Disclosure (Confidentiality) which means something is hidden, and Tampering (Integrity) which means it is not writable.

3. Attack Vectors: The hardware that would be used to protect the secret would be fabricated by someone in a factory. The factory will either program the secret onto the hardware or send the hardware to the company with memory for read access in one component and write access in another component so that the company can program the hardware and destroy the write component to avoid rewriting. This approach can't be used for all hardware. For example, subway cards need to be rewritten to every month so in that case, the terminals have write access to the card but the user doesn't have write access so it can't be overwritten by the user. To fabricate the hardware, the laboratory/factory needs to be trusted. And to prove they are trustworthy, the laboratory gets certified. The certification body sends people in, to audit them, check out the employees and their procedures and conclude whether the laboratory is trusted or not.

4. **Supply Chain**: After the hardware has been made, it will be shipped to stores that will sell it or it is shipped to the consumers from the store. During shipping it could be intercepted by the attackers and tampered with, then re-packaged without the knowledge of the store or the consumers. Also, some attacks can be performed on point of sale terminals when some insider (employees) have access to the terminals and tampered with it in the warehouse

5. Accidents: there are a lot of memory based devices (e.g. USB Keys, Digital picture frames) which may contain malware in them accidentally, which could affect the system of the user. The company that created this hardware may not be aware of the malware on the device. Examples of companies that had this kind of

accidents are IBM, Dell, Samsung, HP, Apple, etc. All the attacks stated above are the main reasons for why the user might get a bad hardware.

# 2.3 Attack Circuits

RFID, Smart Card, Micro- Controller, ASICS, FPGAs RFID is passive, a signal can be sent to it and it responds. It can't be programmed; it can't perform any computations based on the signal sent to it. Smart card, on the other hand, performs computations based on what was sent to it. Micro-controller is like an ID with no chip, ASCIS are fabricated circuits that are custom made to do implementations so all your processors and memories are on ASICS. ASICS are expensive because they are custom made, and before the design is committed to ASICS, a lot of testing will be done with FPGAs to make sure that circuit actually works. FPGAs are programmable chips. When the chip is bought, its blank and it can be programmed with software to do whatever you want. They are not as fast as ASCIS because they are general purpose. FPGAs are faster than software but slower than ASCIS. Why are we attacking Circuits? The main reason for attacking circuits is to recover a secret that had been encoded on a piece of hardware or for the attacker to program a certain value to the circuit. The secret could be the actual algorithm itself. Some attackers reverse engineer the algorithm of the RFID or Smart Card to find flaws in the algorithm itself. This is because some developer wants to keep the algorithm used to protect the circuit a secret due to the fact that the developers are not using a standard algorithm. The algorithm used should be a standard algorithm so as to know how to better protect it. The Circuit attacks are:

1. **Black Box Testing:** To perform this attack, the attacker sends an input to the circuit and receives an output. Based on the input and output behavior, the attacker will decide what kind of algorithm to used. An example is Speed Gas RFID which are proprietary stream cipher. The attackers found the documentation and modified it to discover the cipher used and break the circuit. This type of attack is non-invasive, meaning that the card/chip will not be destroyed when probed so it can be used another time. Another method that can be used in black boxing is fuzzing in software security which allows large random inputs to the circuit and get strange responses like undocumented features, factory testing, etc.

2. **Physical Probing:** To perform this attack the attacker sticks a probe unto the chip itself and reads data off the chip. Within a circuit, there is a wire that connects components to each other called the bus and the bus is where the information would be read as the data is moving around in the bus. The data can also be read off the memory location in the circuit. The probe can have a submission precision and it's an invasive method. A lot of circuits are driven by a clock, and if the attacker can slow down the clock it gives a lot of time to the attacker to read the voltage of the circuit

. 3. **Reverse Engineering:** To perform this attacker, the attacker must acquire the smart card and physically expose the circuit. The smart card is manufactured with different layers and each layer is removed until the

physical circuit is exposed. The attacker then takes high resolution photographs of the circuit and uploads it to a computer and uses a code and machine learning application to figure out what the actual circuit does. Once the circuit is figured out, then the algorithm used in the smart card also is exposed and the algorithm can be broken. An example of a smart card where the reverse engineering attack was performed on is the Mifare (Subway card).

4. **Fault Generation:** Some technologies fail. E.g. A TV providers sends a message to the client asking if the clients wants to renew the subscription. If TV providers don't receive a message NO from the clients, they don't disconnect, so the clients are granted access. So some clients can just cut the power at the right time to prevent the response to the TV providers, since they won't disconnect with no response. This is a non-invasive attack. Other things that can be done are modifying the memory contents (non-invasive), glitch (rapid change) the power or clock (non-invasive), heating up components e.g. with a user (semi- invasive), modify chip e.g. cutting wires (invasive) etc.

5. Side Channel Analysis: To perform this attack, the attackers makes use of the hardware normally but makes sensitive measure of certain things and based on the measurements done, the attacker can infer secrets. An example of things to measure is power (the amount of voltage in an ATM), timing analysis in cryptography (software effect), electromagnetic emission, acoustic sounds (performed on RSA). These are called side channel because they are outside the normal channels. They are non-invasive. It is slower than the normal attacks.

#### 2.4 Counter Measures

- 1. Obfuscate data (Scramble, encrypt) on buses

- 2. Obfuscate the ASICS layout, 3D stacking

- 3. Metal mesh on top of the circuit (if the circuit is probed, it causes a short and the memory resets)

- 4. Side Channel: physical shields, asynchronous circuits.

Also, a decrease in the signals from the circuits of the hardware like the noise or add artificial noise or low the circuit's power METHODOLOGIES There is no good methodology for hardware (that means no static analysis or dynamic analysis of hardware). It is an open question that needs to be researched on. Most of it has to do with domain specific knowledge and it is advisable to follow the requirement engineering process. Common criteria/NIST has protection profiles which provide the properties not how to achieve them.

#### 2.5 Hardware Trojan:

A hardware Trojan can be described as a malicious alteration or inclusion to an integrated circuit (IC) that will either alter its intended function or cause it to perform an additional malicious function.

# Fig 2.1: Block Diagram of Hardware Trojan Inserted Circuit

These malicious inclusions or alterations are generally programmed to activate only under a specific set of circumstances created by an attacker and are extremely hard to detect when in their dormant state.

Block diagram of typical hardware Trojan inserted circuit is shown in fig2. 1.

As technology advances, so does the demand for IC boards leaving many technology companies without the resources to produce secure enough ICs to meet current demands.

This has pushed companies into the 'fabless' trend prevalent in today's semi-conductor industry, where companies are no longer attempting to produce the goods in their own factories, but instead are outsourcing the process to cheaper factories abroad .This growth brings with it a significant rise in the level of threat posed by hardware Trojans, a threat that directly affects all companies concerned with products that utilize ICs. This encompasses many different industries, including the military and telecommunications companies, and can potentially affect billions of devices from mobile phones and computers to military grade aviation and detection devices, particularly at a time when wireless devices are being introduced as links in critical infrastructure, compounding trust and security issues even further.

### 2.5.1 Action Characteristics:

The action characteristics of a hardware Trojan refer to the effect the Trojan will have on the execution of its payload. Hardware Trojans will typically fall into one of two categories: implicit or explicit. Implicit Trojans will not change the board's circuitry of the IC; instead, they will perform their malicious function in tandem with the intended function of the board. This makes these Trojans easier to detect as they tend to cause small path delays on activation and consume more power whilst active.

In contrast, an explicit Trojan will change the function of the board's circuitry on activation. This can come in the form of a signal alteration or even leaking of information via predefined board pins. These Trojans tend to cause distinct path delays as well as large changes in circuit's capacity

Hardware Trojan Detection requires overcoming numerous challenges. Namely:

1. Handling large architectures.

2. Being non-destructive to the IC.

3. Being cost effective.

4. Ability to detect Trojans of all sizes.

- 5. Authenticating chips in as small a time frame as possible.

- 6. Dealing with variations in manufacturing processes.

- 7. Detecting all Trojan classifications.

8. Detecting Trojans in a reasonable time frame.

There is no single method capable of detecting all types of Hardware Trojans, nor overcoming all the challenges described here-above. Over the years, several methods have been developed to detect different types of Trojans. These methods are described here-after.

Physical Inspection One of the most obvious method of detection is physical inspection of the board itself. This method is sometimes classified as a failure analysis based technique. Those techniques usually comprise two steps:

- (1) Cutting and lifting the molding coat to expose the circuitry; and

- (2) Performing various scans

Functional Testing Often referred to as Automatic Test Pattern Generation (ATPG) this technique is more commonly used to locate manufacturing faults; it has been shown to be effective in detecting hardware Trojans. ATPG involves inputs of ports are stimulated and then the output ports are monitored for variations that may indicate a hardware Trojan has been activated. Functional testing techniques can also be useful when attempting to determine the trigger patterns of conditional Trojans. Built-In-Self-Test Techniques Built- In-Self-Test (BIST) techniques are commonly used to detect manufacturing faults and are present in many chips. If unknown or malicious logic is detected during these tests a bad checksum result is given, although designed to detect manufacturing faults on some occasions these tests can detect hardware Trojans

Side channel analysis techniques are some of the most commonly used procedures in hardware Trojan detection. These techniques generally measure signals such as power and path delay, looking for fluctuations potentially caused by Trojans. Side channel analysis can have a high success rate as even in a dormant state the Trojans trigger signal will cause some current leakage

3. Methodology: In order to carry out the investigation our Trojan was designed and loaded onto an Basys 3 Artix 7 FPGA board.

Three different detection techniques are demonstrated, the first utilises power analysis techniques as well as side channel analysis, allowing security investigators to measure both the power variance, traces and current leakage, followed by a concentrated heat measurements using an infrared thermometer, and finally a thermal camera test is carried out. The three experiments are carried out using off-the-shelf hardware and are applied to both the Trojan-free and Trojan-inserted designs. Attempts are then made to detect the trojan in its dormant form. While in in their dormant form Trojans do not perform any malicious actions, however, wait

to be activated, through an activation signal, this can be done through the push of a button, or through a specific set of instructions. It is however important to be able to detect trojans in their dormant form, before they activate and perform malicious actions.

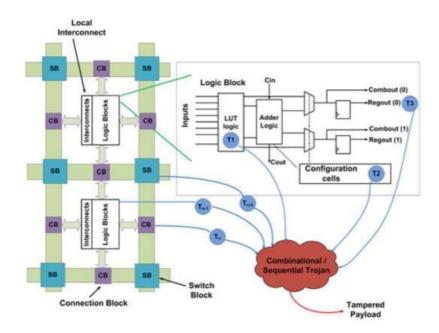

Fig: 2.2 Simplified architecture of an FPGA showing the trigger points that a Trojan may use.

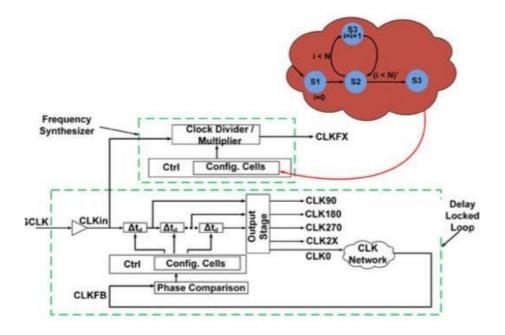

Fig: 2.3 Simplified schematic of digital clock manager (DCM) in Xilinx's Virtex-5 FPGA device

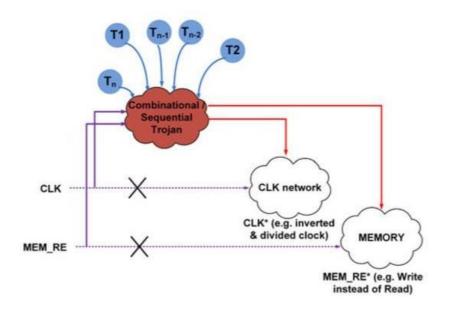

*Fig: 2.4Diagram showing examples of payloads that can be altered by an implanted Trojan circuit.*

### 2.5.2 Payload Characteristics

Hardware Trojans can also be classified based on their intended behaviour. Trojans can be inserted for causing malfunction or for leaking sensitive information. In the former case, Trojans alter the functionality of the design in some way, while Trojans designed for leaking sensitive information may do so without modifying the logic functionality of the design.

Trojans for Malfunction can be further classified into two subcategories based on whether they cause logical malfunction or physical malfunction. Trojans presented in the previous sections cause logic malfunction by modifying the values in the LUTs, causing undesired routing between two logic modules, etc. Fig.2.4 shows additional examples of payloads affected by Trojans.

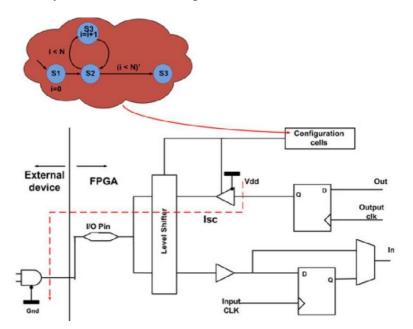

Trojans intended to cause physical damage can create electrical conflicts at the I/O ports or at the programmable interconnects. Consider the programmable I/O block in Fig. 2.5. When an I/O port is configured to be an input by a design, the configuration cells in the I/O block should disable the output block to prevent internal conflicts. A counter-based Trojan can be inserted in the foundry which detects the state of the I/O port and begins counting. When the counter counts to the final value, the Trojan may enable the output logic when the port is configured as an input. This would cause a high short-circuit current to flow between the FPGA and the external device, possibly damaging the system. These Trojans are similar to the MELT viruses described in except that Trojans causing physical destruction may also be inserted in the foundry.

Since IP designs involve a high development cost and contain sensitive information, security is of utmost importance many high-end FPGAs such as Xilinx's Virtex4 and Virtex5, and Altera's StratixII and StratixIII offer bit-stream encryption to prevent unauthorized cloning of the bit-stream. Fig.2.6 shows the

security features in a generic FPGA device that contains the programmable logic array configuration logic which controls the programming of the SRAM cells in the logic array, interconnect network, and additional modules in the device. The device also contains a decryption module for decrypting the bit-stream using a key stored in a non-volatile memory. Security measures in the device

(1) Prevent the key from being read and sent to a port by clearing the configuration data and keys when a read attempt is made,

(2) Prevent read-back of the configuration data, and

(3) Restrict decryption access after configuration.

However, all of these measures only prevent malicious code in an IP from accessing the key or configuration data. Hardware Trojans can leak the IP in two ways: by leaking the decryption key, or by leaking the design itself. An attacker in the foundry can insert an extraneous circuit (Fig. 2.6) to tap the wires connecting the non-volatile memory and decryption module. Even if the decryption module is implemented in the logic array by using a decryption bit-stream as mentioned in , such an instantiated module must have access to the non-volatile key for decryption. A copy of the key can be stored in the Trojan, which may then leak it through side-channels or covert-channels. Using side-channels, a Trojan can hide the key in the power traces or by emitting electromagnetic radiation containing the information and an attacker can observe these signals to steal the key. For example, the MOLES Trojan presented in uses a spread-spectrum technique to leak the key in the power traces over several clock cycles. Alternatively, a Trojan may also multiplex the JTAG port, USB port, or any other programming port to leak the key through covert channels when the ports are not being used. Since SRAM-based FPGAs are volatile, an external device must be used to store the encrypted design. If an adversary is in possession of the FPGA device loaded with the design, the encrypted bit-stream can be stolen by dropping the connection between an FPGA's programming ports and the external device storing the encrypted bit-stream. In other cases, a Trojan may fake a request to the external device to send the programming data to the FPGA. This time, however, the Trojan MUXes the bit-stream and rather than sending it to the decryption, it may store blocks of the bit-stream at any given time and leak them through side-channels or covert-channels.

#### 2.5.3 Trojans in CLB/EMB FPGA

Configurable logic blocks (CLBs) and embedded memory blocks are highly flexible, but require significant configuration to implement the desired functions. This severely harms the memory or logic integration density in FPGA which makes it more amenable for Trojan insertion. Fig.2.7 shows a FPGA CLB, which can act as a 2-input look up table, a 4-bit Random Access Memory (RAM), or a 4-bit shift register. In Fig2.7a the inserted Trojan has been shown in red: the trigger condition is derived from the memory content of two consecutive RAM locations, and can harm the shift register functionality or the write

enable functionality of the memory block at run-time. The trigger condition can also be generated from the output of other CLBs, or alternatively can be derived from the output of other functional units. Fig.2.7b shows a Trojan instance inserted inside an embedded memory block in a commercial FPGA device. Similar to a CLB, an EMB is also capable of executing functionalities like shift register, FIFO etc. in addition to acting as Random Access Memory. The control circuitry shown in Fig2.7b decides between normal read operation and shift register operation inside the EMBs. The inserted logic or Trojan conditionally affects the shift operation inside a EMB by using adjacent memory contents and so can be triggered at run-time. It can be noted that the similar trigger conditions can also be effectively used to leak the contents of the memory to the output port. Such malfunctions can be achieved by changing the address bits of the memory blocks in different clock cycles and reading out the immediate next location of the memory in each and every cycle so as to obtain the complete memory contents stored in a particular EMB or a set of EMBs.

Fig 2.5 Programmable I/O block containing hardware Trojans to cause logical and electrical malfunction.

Fig 2.6 FPGA device with security features for bit-stream decryption.

*Fig: 2.7 Hardware Trojan inside: (a) a configurable logic block (CLB) and (b) an embedded memory block (EMB) of FPGA.*

# 2.5.4 Types of Hardware Trojans:

There are different types of hardware Trojans like Combinational, Sequential and Hybrid Trojans as shown in fig2.8

# **Types of Hardware Trojan**

Fig2.8: Types of Hardware Trojans

# 2.5.5 Example Attack

The example attack is on a CHIP & PIN. The attack is CICA 2000 and it was performed in the United Kingdom. It's actually a protocol attack, but in order to perform it, you need customized hardware. The basic hardware used is the bank card. The bank card might have been stolen and the attacker didn't

know the pin to the card, but wants to buys something with the card without the pin. This attack can't be performed on an ATM because it uses a different protocol, it can only be performed on a handout terminals at a store.

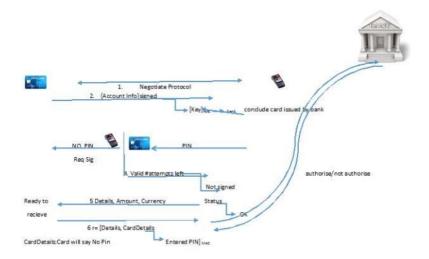

Fig2.9 Simplified diagram of Protocol used

# Issues of this attack

- 1. The Pin (Invalid not signed)

- 2. Details used in the protocol is not enough

- 3. Card Detail : Terminal can't parse only bank.

# 2.6 Real Life Implementation

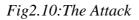

The attacker would need the stolen card, a card reader, a laptop, a circuit (FPGA), wire and a fake card.

Fig2.11: Real life implementation of Chin & Pin attack

In the diagram above, the attacker would stick the card in a card reader and the card reader is placed in a computer, the computer is connected to a circuit like an FPGA. The attacker then have a wire that runs to a fake bank card that is in the terminal. The wire is attached to the circuit which was attached to the computer that the card reader which contains the real card is inserted. This is the Man-in-the-middle device, the stolen card would transfer all the information on the card to the fake card in the terminal. To perform this attack in real life, all the equipment would be placed in a bag pack and the wire would be passed inside the cloth and since by law the cashier is not supposed to touch the card, the fake card is inserted with the wire on the circuit and the attack is performed. This attacked happened in the UK but this kind of attack cannot happen in Canada.

#### **CHAPTER 3**

### **INTRODUCTION TO FPGA**

#### 3.1 What is FPGA?

A field-programmable gate array (FPGA) is designed to be configured by a customer or a designer after manufacturing – hence the term "field-programmable". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). Circuit diagrams were previously used to specify the configuration, but this is increasingly rare due to the advent of electronic design automation tools.

FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together", like many logic gates that can be inter-wired in different configurations. Logic block-scan be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory. Many FPGAs can be reprogrammed to implement different logic functions allowing flexible reconfigurable computing as performed in computer software.

#### 3.2 THEORY

Altera was founded in 1983 and delivered the industry's first reprogrammable logic device in 1984 – the EP300 – which featured a quartz window in the package that allowed users to shine an ultra-violet lamp on the die to erase the EPROM cells that held the device configuration. In December 2015, Intel acquired Altera.

Xilinx co-founders Ross Freeman and Bernard Vonderschmitt invented the first commercially viable field-programmable gate array in 1985 – the XC2064. The XC2064 had programmable gates and programmable interconnects between gates, the beginnings of a new technology and market. The XC2064 had 64 configurable logic blocks (CLBs), with two three-input lookup tables (LUTs). More than 20 years later, Freeman was entered into the National Inventors Hall of Fame for his invention.

Notes:

1. Each 7 series FPGA slice contains four LUTs and eight flip-flops; only some slices can use their LUTs as distributed RAM or SRLs.

2. Each DSP slice contains a pre-adder, a 25 x 18 multiplier, an adder, and an accumulator.

20

3. Block RAMs are fundamentally 36 Kb in size; each block can also be used as two independent 18 Kb blocks.

- 4. Each CMT contains one MMCM and one PLL.

- 5. Artix-7 FPGA Interface Blocks for PCI Express support up to x4 Gen 2.

- 6. Does not include configuration Bank 0.

- 7. This number does not include GTP transceivers.

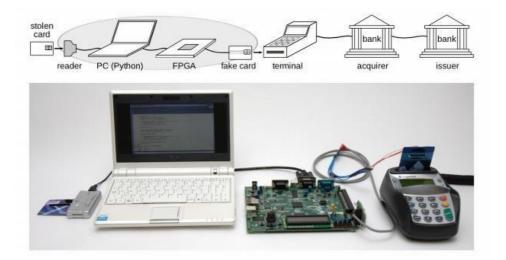

Fig3.1 Xilinx Artix 7 FPGA Trainer kit

| Callout | Component Description                    | Callout | Component Description                |

|---------|------------------------------------------|---------|--------------------------------------|

| 1       | Power select jumper and battery header   | 13      | FPGA configuration reset button      |

| 2       | Shared UART/ JTAG USB port               | 14      | CPU reset button (for soft cores)    |

| 3       | External configuration jumper (SD / USB) | 15      | Analog signal Pmod port (XADC)       |

| 4       | Pmod port(s)                             | 16      | Programming mode jumper              |

| 5       | Microphone                               | 17      | Audio connector                      |

| 6       | Power supply test point(s)               | 18      | VGA connector                        |

| 7       | LEDs (16)                                | 19      | FPGA programming done LED            |

| 8       | Slide switches                           | 20      | Ethernet connector                   |

| 9       | Eight digit 7-seg display                | 21      | USB host connector                   |

| 10      | JTAG port for (optional) external cable  | 22      | PIC24 programming port (factory use) |

| 11      | Five pushbuttons                         | 23      | Power switch                         |

| 12      | Temperature sensor                       | 24      | Power jack                           |

Fig3.2 Port numbers of Artix7 FPGA Trainer kit

# Table 3.1: Artix-7 FPGA Feature Summary by Device

|        |       | Configur  | able Logic  |    |     |     |       |    |   |    |   |    |     |

|--------|-------|-----------|-------------|----|-----|-----|-------|----|---|----|---|----|-----|

|        |       |           | Max         |    |     |     |       |    |   |    |   |    |     |

|        |       | Slices(1) | Distributed |    | 18  | 36  | Max   |    |   |    |   |    |     |

| XC7A12 | 12,80 | 2,000     | 171         | 40 | 40  | 20  | 720   | 3  | 1 | 2  | 1 | 3  | 150 |

| XC7A15 | 16,64 | 2,600     | 200         | 45 | 50  | 25  | 900   | 5  | 1 | 4  | 1 | 5  | 250 |

| XC7A25 | 23,36 | 3,650     | 313         | 80 | 90  | 45  | 1,620 | 3  | 1 | 4  | 1 | 3  | 150 |

| XC7A35 | 33,28 | 5,200     | 400         | 90 | 100 | 50  | 1,800 | 5  | 1 | 4  | 1 | 5  | 250 |

| XC7A50 | 52,16 | 8,150     | 600         | 12 | 150 | 75  | 2,700 | 5  | 1 | 4  | 1 | 5  | 250 |

| XC7A75 | 75,52 | 11,800    | 892         | 18 | 210 | 105 | 3,780 | 6  | 1 | 8  | 1 | 6  | 300 |

| XC7A10 | 101,4 | 15,850    | 1,188       | 24 | 270 | 135 | 4,860 | 6  | 1 | 8  | 1 | 6  | 300 |

| XC7A20 | 215,3 | 33,650    | 2,888       | 74 | 730 | 365 | 13,14 | 10 | 1 | 16 | 1 | 10 | 500 |

Table3. 2: Artix-7 FPGA Device-Package Combinations and Maximum I/Os

| Packa | CP | G23  | CP | G23  | CSG32 |         | CSG32 |         | CSG32 CSG32 |         | FTG25 |         | SBG48 |         | FGG4 |         | FBG48 |      | FGG6    |     | FBG67   |     | FFG11   |  |

|-------|----|------|----|------|-------|---------|-------|---------|-------------|---------|-------|---------|-------|---------|------|---------|-------|------|---------|-----|---------|-----|---------|--|

| Size  | 10 | x 10 | 10 | x 10 | 15    | 15 x 15 |       | 15 x 15 |             | 15 x 15 |       | 17 x 17 |       | 19 x 19 |      | 23 x 23 |       | x 23 | 27 x 27 |     | 27 x 27 |     | 35 x 35 |  |

| Ball  |    |      |    |      |       |         |       |         |             |         |       |         |       |         |      |         |       |      |         |     |         |     |         |  |

|       |    | I/O  |    | I/O  |       | I/O     |       | I/O     |             | I/O     |       | I/O     |       | I/O     |      | I/O     |       | I/O  |         | I/O |         | I/O |         |  |

|       |    | HR   |    | HR   |       | HR      |       | HR      |             | HR      |       | HR      |       | HR      |      | HR      |       | HR   |         | HR  |         | HR  |         |  |

| XC7A  |    |      | 2  | 112  |       |         | 2     | 150     |             |         |       |         |       |         |      |         |       | _    |         |     |         |     |         |  |

|       |    |      |    |      |       |         |       |         |             |         |       |         |       |         |      |         |       |      |         |     |         |     |         |  |

| 12T   |    |      |    |      |       |         |       |         |             |         |       |         |       |         |      |         |       |      |         |     |         |     |         |  |

|       |    |      |    |      |       |         |       |         |             |         |       |         |       |         |      |         |       |      |         |     |         |     |         |  |

| XC7A  | 2  | 106  |    |      | 0     | 210     | 4     | 150     | 0           | 170     |       |         | 4     | 250     |      |         |       |      |         |     |         |     |         |  |

| XC7A  |    |      | 2  | 112  |       |         | 4     | 150     |             |         |       |         |       |         |      |         |       |      |         |     |         |     |         |  |

| XC7A  | 2  | 106  |    |      | 0     | 210     | 4     | 150     | 0           | 170     |       |         | 4     | 250     |      |         |       |      |         |     |         |     |         |  |

| XC7A  | 2  | 106  |    |      | 0     | 210     | 4     | 150     | 0           | 170     |       |         | 4     | 250     |      |         |       |      |         |     |         |     |         |  |

| XC7A  |    |      |    |      | 0     | 210     |       |         | 0           | 170     |       |         | 4     | 285     |      |         | 8     | 300  |         |     |         |     |         |  |

| XC7A  |    |      |    |      | 0     | 210     |       |         | 0           | 170     |       |         | 4     | 285     |      |         | 8     | 300  |         |     |         |     |         |  |

| XC7A  |    |      |    |      |       |         |       |         |             |         | 4     | 285     |       |         | 4    | 285     |       |      | 8       | 400 | 16      | 500 |         |  |

1. All packages listed are Pb-free (SBG, FBG, FFG with exemption 15). Some packages are available in Pb option.

- 2. Devices in FGG484 and FBG484 are footprint compatible.

- 3. Devices in FGG676 and FBG676 are footprint compatible.

- 4. GTP transceivers in CP, CS, FT, and FG packages support data rates up to 6.25 Gb/s.

5. HR = High-range I/O with support for I/O voltage from 1.2V to 3.3V.

### **1. Power Supplies:**

The Nexys 4 board can receive power from the Digilent USB-JTAG port (J6) or from an external power supply. Jumper JP3 (near the power jack) determines which source is used. All Nexys 4 power supplies can be turned on and off by a single logic-level power switch (SW16). A power-good LED (LD22), driven by the "power good" output of the ADP2118 supply, indicates that the supplies are turned on and operating normally.

# 2. FPGA Configuration:

After power-on, the Artix-7 FPGA must be configured (or programmed) before it can perform any functions. You can configure the FPGA in one of four ways:

1. A PC can use the Digilent USB-JTAG circuitry (portJ6, labeled "PROG") to program the FPGA any time the power is on.

2. A file stored in the nonvolatile serial (SPI) flash device can be transferred to the FPGA using the SPI port.

3. A programming file can be transferred to the FPGA from a micro SD card.

4. A programming file can be transferred from a USB memory stick attached to the USB HID port.

The FPGA is made of SRAM (Volatile Memory) so the data configured inside FPGA lost at power Off state. FPGA Configuration is the process of loading the FPGA chip with Configuration data through external devices during power On state.

The Method of Configuring FPGA Can be divided into

- Master Mode

- Slave Mode

- JTAG Mode

# **Master Modes**

In the Master Mode the Configuration data is stored in external nonvolatile memories such us SPI FLASH, Parallel FLASH, PROM and so on. During configuration process the data is loaded in the FPGA Configurable Logic Blocks to operate as a specific application. The configuration clock is provided by FPGA in Master Mode operation.

Fig 3.3 FPGA Configure through External PROM

Fig 3.4FPGA Configure through SPI FLASH Memory

Fig 3.5 FPGA Configure through Internal FLASH

# **Slave Mode**

In Slave Mode, The entire configuration Process is controlled by External device. Those External device may be of processor, Microcontroller, and so on. The configuration can perform serially or parallel method. The Clock input is supplied by the external device for Slave mode.

Fig 3.6: Slave Mode

# **JTAG Connection**

The four-wire JTAG interface is common on board testers and debugging hardware. FPGA mainly uses JTAG interface for prototype download and debugging. JTAG consists of TCK, TMS, TDI and TDO lines for communication.

Fig 3.7: JTAG connection

#### 3. Memory:

The Nexys 4 board contains two external memories: a 128Mbit Cellular RAM (pseudo-static DRAM) and a 128Mbit non-volatile serial Flash device. The Cellular RAM has an SRAM interface, and the serial Flash is on a dedicated quad-mode (x4) SPI bus. The connections and pin assignments between the FPGA and external memories

#### 4. Ethernet PHY:

The Nexys 4 board includes an SMSC 10/100 Ethernet PHY (SMSC part number LAN8720A) paired with an RJ-45 Ethernet jack with integrated magnetic. The SMSC PHY uses the RMII interface and supports 10/100 Mb/s. At power-on reset, the PHY is set to the following defaults:

- RMII mode interface

- Auto-negotiation enabled, advertising all 10/100 mode capable

- PHY address=00001

#### 3.3 Overview of FPGA

The Nexys4 DDR board is a complete, ready-to-use digital circuit development platform based on the latest Artix-7<sup>TM</sup> Field Programmable Gate Array (FPGA) from Xilinx®. With its large, high-capacity FPGA (Xilinx part number XC7A100T-1CSG324C), generous external memories, and collection of USB, Ethernet, and other ports, the Nexys4 DDR can host designs ranging from introductory combinational circuits to powerful embedded processors. Several built-in peripherals, including an accelerometer, temperature sensor, MEMs digital microphone, a speaker amplifier, and several I/O devices allow the Nexys4 DDR to be used for a wide range of designs without needing any other components.

The Artix-7 FPGA is optimized for high performance logic, and offers more capacity, higher performance, and more resources than earlier designs. Artix-7 100T features include:

- 15,850 logic slices, each with four 6-input LUTs and 8 flip-flops

- 4,860 Kbits of fast block RAM

- Six clock management tiles, each with phase-locked loop (PLL)

- 240 DSP slices

- Internal clock speeds exceeding 450 MHz  $\square$  On-chip analog-to-digital converter (XADC)

The Nexys4 DDR also offers an improved collection of ports and peripherals, including:

- 16 user switches

- 16 user LEDs

- Two 4-digit 7-segment displays

- USB-UART Bridge

- Two tri-color LEDs

- Micro SD card connector

- 12-bit VGA output

- PWM audio output

- PDM microphone

- 3-axis accelerometer

- Temperature sensor

- 10/100 Ethernet PHY

- 128MiB DDR2

- Serial Flash

- Four Pmod ports

- Pmod for XADC signals

- Digilent USB-JTAG port for FPGA programming and communication

- USB HID Host for mice, keyboards and memory sticks

The Nexys4 DDR is compatible with Xilinx's new high-performance Vivado® Design Suite as well as the ISE® toolset, which includes ChipScope<sup>™</sup> and EDK. Xilinx offers free WebPACK<sup>™</sup> versions of these toolsets, so designs can be implemented at no additional cost. The Nexys4 DDR is not supported by the Digilent Adept Utility.

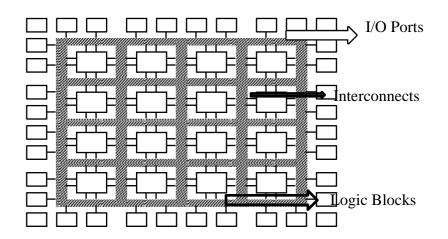

- Logic blocks

- to implement combinational and sequential logic

- Interconnect

- wires to connect inputs and outputs to logic blocks

- I/O blocks

- special logic blocks at periphery of device for external connections

- Key questions:

- How to make logic blocks programmable?

- How to connect the wires?

- After the chip has been fabricated?

Fig3.8 Block diagram of FPGA

# 3.4 Programmability of FPGAs:

- User programmability of CPLDs and FPGAs is achieved via user-programmable switch technologies.

- For CPLDs, floating-gate transistors are used like EPROM or EEPROM. On the other hand, FPGAs normally use SRAM (static RAM) or anti fuse technology.

- Properties of the switches, such as, size, on-resistance, and capacitance dictate trade-offs in architecture.

- In SRAM based FPGAs, there is an SRAM bit corresponding to each of the programmable points within the device.

- When the device is powered-on or reset, it reads a configuration program from an off-chip memory and loads it into on-chip SRAM.

- The configuration program defines the logic function realized by individual logic blocks and interconnections.

- Devices using SRAM based switching can be reprogrammed easily by just changing the configuration program.

- FPGAs belonging to Xilinx, Plassey, Algotronix, Concurrent Logic, Toshiba, etc. are SRAM based.

- SRAM provides fast re-programmability at the cost of large area (at least five transistors for cell and one for switch).

| Name      | Whether             | Whether volatile | Technology |

|-----------|---------------------|------------------|------------|

|           | reprogrammable      |                  |            |

| Fuse      | No                  | No               | Bi-polar   |

| EPROM     | Yes, out of circuit | No               | UVCMOS     |

| EEPROM    | Yes, in circuit     | No               | EECMOS     |

| SRAM      | Yes, in circuit     | Yes              | CMOS       |

| Anti FUSE | No                  | No               | CMOS+      |

### **Comparison between programming techniques**

Table3.3 Comparison between programming techniques

## 3.5 FPGA Logic Blocks

- There are wide variations in the logic block structure of FPGAs available from different vendors.

- They vary in number of inputs and outputs, amount of area consumed, complexity of logic functions that they can realize, total number of transistors needed, and so on.

- The logic blocks can broadly be classified into the following two categories Fine Grain, Coarse Grain

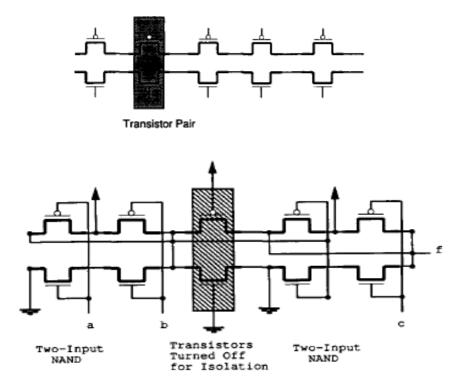

### **Fine Grain Logic Block**

- The block contains a few transistors that can be interconnected via programming.

- Cross point FPGA uses a single transistor pair for each Boolean variable in the logic block.

Fig3.9 Schematic diagram of FPGA Logic blocks

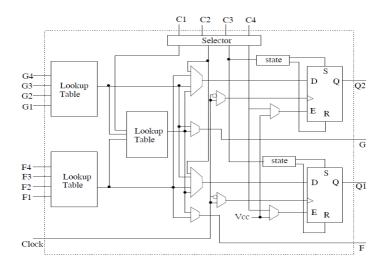

# Coarse Grain Block – XC4000 from Xilinx

Fig3.10 Schematic diagram of coarse grain block

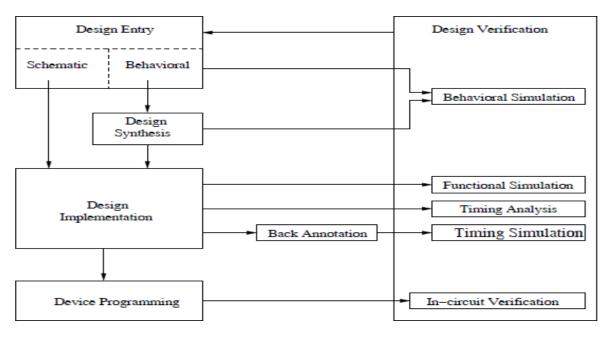

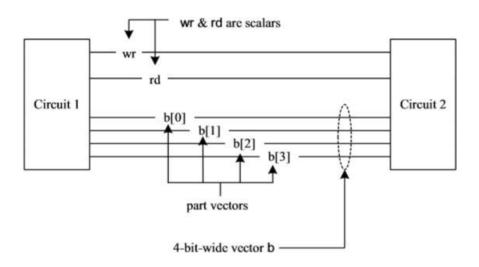

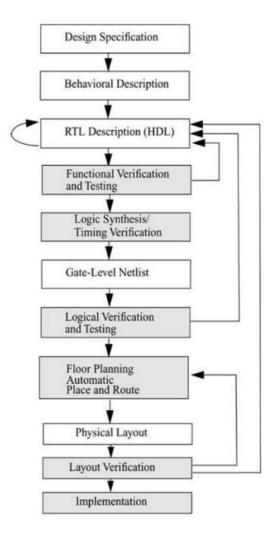

### **FPGA Design Flow**

Fig3.11 Schematic diagram of FPGA Design flow

## 3.6 Modern FPGA's

- In addition to the basic blocks (such as, logic blocks, I/O blocks and interconnects), modern FPGAs have additional units that make the design process simpler and more efficient.

- The two major system components, difficult to implement in FPGAs are embedded memories and blocks for arithmetic calculations.

- Amongst the various calculations, multiplication is the most widely used one. Most of the modern FPGAs contain embedded logic blocks for multiplication and memories to hold data. DSP functionalities are highly facilitated by the availability of these.

- In many applications, FPGAs need to communicate with microprocessors. This has motivated many FPGA vendors to embed soft processor cores within FPGAs. This reduces the latency of communication between the microprocessor and the FPGA.

### CHAPTER4

### Verilog Hardware Description Language

#### 4.1 What is HDL

Hardware description language (HDL) is a specialized computer language used to program electronic and digital logic circuits. The structure, operation and design of the circuits are programmable using HDL. HDL includes a textual description consisting of operators, expressions, statements, inputs and outputs. Instead of generating a computer executable file, the HDL compilers provide a gate map. The gate map obtained is then downloaded to the programming device to check the operations of the desired circuit. The language helps to describe any digital circuit in the form of structural, behavioural and gate level and it is found to be an excellent programming language for FPGAs and CPLDs. The three common HDLs are Verilog, VHDL, and SystemC.

#### 4.2 Importance of HDLs

HDLs have many advantages compared to traditional schematic-based design.

• Designs can be described at a very abstract level by use of HDLs. Designers can write their RTL description without choosing a specific fabrication technology. Logic synthesis tools can automatically convert the design to any fabrication technology. If a new technology emerges, designers do not need to redesign their circuit. They simply input the RTL description to the logic synthesis tool and create a new gate-level net-list, using the new fabrication technology. The logic synthesis tool will optimize the circuit in area and timing for the new technology.

• By describing designs in HDLs, functional verification of the design can be done early in the design cycle. Since designers work at the RTL level, they can optimize and modify the RTL description until it meets the desired functionality. Most design bugs are eliminated at this point. This cuts down design cycle time significantly because the probability of hitting a functional bug at a later time in the gate-level netlist or physical layout is minimized.

• Designing with HDLs is analogous to computer programming. A textual description with comments is an easier way to develop and debug circuits. This also provides a concise representation of the design, compared to gate-level schematics. Gate-level schematics are almost incomprehensible for very complex designs.

### 4.3 Introduction to Verilog HDL

Verilog HDL is one of the two most common Hardware Description Languages (HDL) used by integrated circuit (IC) designers. The other one is VHDL. HDL's allows the design to be simulated earlier in the design cycle in order to correct errors or experiment with different architectures. Designs described in HDL are technology-independent, easy to design and debug, and are usually more readable than schematics, particularly for large circuits.

Verilog can be used to describe designs at four levels of abstraction:

- (i) Algorithmic level (much like c code with if, case and loop statements).

- (ii) Register transfer level (RTL uses registers connected by Boolean equations).

- (iii) Gate level (interconnected AND, NOR etc.).

(iv)Switch level (the switches are MOS transistors inside gates). The language also defines constructs that can be used to control the input and output of simulation.